[0x00] Concept

메뉴얼 순서 상 드디어 마지막 챕터입니다. 물론 구현을 하면서 더 상세한 내용이 필요할 것 입니다.

해당 챕터에서는 VMX Operation 을 위한 주소 변환을 지원하는 VPID(Virtual-Processor Identifier) 와 EPT(Extended Page-Table 의 메커니즘에 대해 설명합니다.

VPID 는 선형 주소 변환을 관리하기 위한 메커니즘이며, EPT 는 선형 주소 변환을 확장시키는 주소 변환 계층을 정의합니다.(augment 의 의미를 확장으로 해석하였습니다.)

해당 내용에 명확한 이해를 위해서는 Intel SDM Vol.3A Chapter 4 Paging 을 어느정도 숙지해야 합니다. 이는 별도의 내용으로 정리 예정입니다.

게스트 물리 주소 와 같이 앞에 게스트가 붙지 않는 이상 호스트의 물리 주소를 의미합니다.[0x01] Virtual Processor Identifiers(VPIDs)

VMX Operation 을 위한 기존의 아키텍처에서는 TLB 및 Paging-Structure Cache 를 플러시하기 위해 VMX Transition 이 필요했습니다.

이를 통해 이전의 선형 주소 공간에 대해 캐시된 변환이 전환 후 사용되지 않도록 보장했습니다.

VPID(Virtual Processor Identifier) 는 논리 프로세서가 여러 선형 주소 공간에 대한 정보를 캐시할 수 있는 기능을 VMX Operation 에 제공합니다.

VPID 를 사용하면 VMX Transition은 캐시된 정보를 유지할 수 있고 논리 프로세서가 다른 선형 주소 공간으로 전환될 수 있습니다.

해당 포스트 내 Caching Translation Information 에서 여러 선형 주소 공간에 대해 캐시 된 정보를 관리하는 메커니즘을 자세히 설명합니다.

논리 프로세서는 16 bit VPID 로 캐시된 일부 정보에 태그를 지정할 수 있습니다.

- 현재

VPID는 아래의 상황에서0000h입니다.VMX Operation이 아닌 경우VMX root operation에 있는 경우Second_enable VPID제어가 0일 때VMX non-root operation에 있는 경우

- 논리 프로세서가

VMX non-root operation에 있고Second_enable VPID제어가 1인 경우 현재VPID는VMCS의VM-execution control field내VPID의 값입니다.(VM Entry는 이 값이0000h가 아님을 보장합니다.)

VPID 는 PCID(Process-Context Identifier) 와 동시에 사용할 수 있습니다. 동시에 사용하게 되면 프로세서는 캐시된 정보를 현재 VPID 와 PCID 를 연결합니다. 이러한 정보는 현재 VPID, PCID 가 모두 캐시된 정보와 관련된 정보와 일치하는 경우에만 사용됩니다.

[0x02] Hypervisor-Managed Linear-Address Translation(HLAT)

HLAT(Hypervisor-Managed Linear-Address Translation) 은 VMX non-root operation 에서 선형 주소가 변환되는 방식을 변경하는 기능입니다.

일반적인 Paging 대신 HLAT Paging 이라는 변경된 프로세스를 사용합니다.

HLAT Paging 은 Tertiary_enable HLAT 제어가 1로 설정된 경우에만 사용됩니다. HLAT Paging 은 4-Level, 5-Level Paging 에서만 사용됩니다.

HLAT Paging 은 일반적인 Paging 을 변경한 것 이기 때문에 4-Level, 5-Level Paging 의 동작을 설명의 경우 별도의 페이징 관련 챕터를 통해 확인할 수 있습니다.

[0x03] The Extended Page Table Mechanism(EPT)

EPT(Extended Page-Table Mechanism) 은 물리 메모리의 가상화를 지원하는 데 사용할 수 있는 기능입니다.

EPT 가 사용 중일 때 일반적으로 물리 주소로 처리되고 메모리에 액세스하는 데 사용되는 특정 주소는 게스트의 물리 주소로 처리됩니다.

게스트 물리 주소는 메모리에 액세스하는 데 사용되는 물리 주소를 생성하기 위해 EPT Paging-Structure 집합을 통해 변환됩니다.

[-] EPT Overview

EPT 는 Second_enable EPT 제어가 1일 때 사용됩니다. VMX non-root operation 에서 사용되고 이벤트 주입(Event Injection)을 위해 VM Entry 에서 사용되는 게스트 물리 주소를 변환합니다.

게스트 물리 주소에서 물리 주소로의 변환은 EPT Paging-Structure(EPT 페이징 구조) 에 의해 결정됩니다. EPT Paging-Structure는 프로세서가 IA-32e mode 에 있는 동안 선형 주소를 변환하는 데 사용되는 구조와 유사합니다.

계속해서 언급 될 EPT Paging-Structure 아래와 같은 구조입니다.

CR0.PG = 1 이면 선형 주소는 CR3 를 통해 참조되는 페이징 구조를 통해 변환됩니다. Second_enable EPT 제어가 1로 설정되어 있는 동안 이러한 페이징 구조를 Guest Paging-Structure(게스트 페이징 구조)라고 합니다.

CR0.PG = 0 이면 게스트 페이징 구조가 없습니다.

Second_enable EPT 제어가 1일 때 게스트 물리 주소의 식별(ID)은 CR0.PG 의 값에 따라 달라집니다.

CR0.PG = 0인 경우 선형 주소는 게스트 물리 주소로 처리됩니다.CR0.PG = 1인 경우 게스트 물리 주소는CR3와 게스트 페이징 구조의 내용에서 파생된 주소입니다.

CR0.PG = 1 인 경우에 선형 주소를 물리 주소로 변환하려면 EPT 를 사용하여 게스트 물리 주소를 여러 번 변환해야 합니다.

예를 들어 CR4.PAE, PSE = 0 인 경우를 가정해보겠습니다. 32 bit의 선형 주소 변환은 아래와 같이 동작합니다.

- 선형 주소의 bits 31:22 는

CR3의 게스트 물리 주소에 위치한 게스트PDE(Page-Directory Entry)를 선택합니다. 게스트PDE의 게스트 물리 주소는EPT를 통해 변환되어 게스트PDE의 물리 주소를 결정합니다. - 선형 주소의 bits 21:12 는 게스트

PDE의 게스트 물리 주소에 위치한 게스트 페이지 테이블 내의 엔트리(PTE)를 선택합니다. 게스트PTE의 게스트 물리 주소는EPT를 통해 변환되어 게스트PTE의 물리 주소를 결정합니다. - 선형 주소의 bits 11:0 은 게스트

PTE의 게스트 물리 주소에 위치한페이지 프레임내의 오프셋입니다. 이 오프셋에 의해 결정된 게스트 물리 주소는EPT를 통해 변환되어 원래 선형 주소가 변환되는 물리 주소를 결정합니다.

추가적으로 EPT 는 게스트 물리 주소를 물리 주소로 변환하는 것 외에도 주소에 액세스 할 때 VMM 이 허용하는 권한을 지정합니다. 허용되지 않는 액세스 시도를 EPT Violation 이라고 하며 VM Exit 의 원인이 됩니다.

해당 내용은 매우 중요하며 본인이 구현할 내용에서 주된 기능이 됩니다. 이를 이용하여 특정 주소에 액세스할 때 VM Exit 를 발생시켜 내가 원하는 동작을 하도록 할 수 있습니다.

프로세서는 게스트 물리 주소가 메모리에 액세스하는 데 사용될 때만 EPT 를 사용하여 게스트 물리 주소를 물리 주소로 변환합니다.

이 내용은 다음을 의미합니다.

MOV to CR3명령은 게스트 물리 주소를CR3에 로드합니다. 해당 주소가EPT를 통해 변환되는지 여부는PAE Paging사용 여부에 따라 달라집니다.PAE Paging을 사용하지 않는 경우, 해당 명령은 메모리에 액세스할 때 해당 주소를 사용하지 않으며EPT를 통해 변환되지 않습니다.(CR0.PG = 1인 경우 주소는 선형 주소를 사용하여 메모리에 액세스한 다음EPT를 통해 변환됩니다.)PAE Paging을 사용하는 경우, 해당 주소에서 4개의PDPTE를 로드하고EPT를 통해 주소를 변환합니다.

PDPTE에는 게스트 물리 주소가 포함되어 있습니다.PDPTE를 로드하는 명령(위의 내용)은 이러한 게스트 물리 주소를 사용하여 메모리에 액세스하지 않으며EPT를 통해 변환되지 않습니다.PDPTE의 주소는 해당PDPTE를 사용하는 선형 주소를 사용하여 액세스한 다음EPT를 통해 변환됩니다.

[-] EPT Translation Mechanism

EPT 변환 메커니즘은 각 게스트 물리 주소의 bits 47:0 만 사용합니다. Page-Walk Length 의 값은 4를 사용하게 되는데, 이는 게스트 물리 주소를 변환하기 위해 최대 4개의 EPT Paging-Structure Entry에 액세스한다는 것을 의미합니다.

이러한 48 bits(변환 메커니즘에 사용되는 게스트 물리 주소)는 EPT Paging-Structure를 트레버스하기 위해 논리 프로세서에 의해 분할됩니다.

아래에서 설명되는 EPT Paging-Structure 와 Paging-Structure 는 다른 구조입니다.

어떠한 오브젝트가 크기에 맞춰 정렬되는 경우를 의미합니다. 8 byte 크기의 데이터는 8의 배수인 주소에 정렬되었을 때 자연스럽게 정렬된 주소로 이해할 수 있습니다. (address % size = 0)

- 4-Kbyte 로 자연스럽게 정렬된(

Naturally aligned)EPT PML4 table은Extended-Page-Table Pointer(EPTP)의 bits 51:12에 지정된 물리 주소에 위치합니다.EPT PML4 Table은 512개의 64bits 로 이루어진 엔트리(EPT PML4E)로 구성됩니다.EPT PML4E는 다음과 같이 정의된 물리 주소를 사용하여 선택됩니다.- (참고 : 링크)

- bits 63:52 는 모두 0입니다.

- bits 51:12 는

EPTP에서 가져온 값 입니다. - bits 11:3 은 게스트 물리 주소의 bits 47:39 입니다.

- bits 2:0 은 모두 0입니다.

EPT PML4E는 게스트 물리 주소의 bits 47:39를 사용하여 식별되므로 게스트 물리 주소 공간의 512-Gbyte 영역에 대한 액세스를 제어합니다. 아래는EPT PML4E에 대한 포맷입니다.

- 4-Kbyte 로 자연스럽게 정렬된

EPTP Table은EPT PML4E의 bits 51:12에 지정된 물리 주소에 위치합니다.EPTP Table은 512개의 64bits 로 이루어진 엔트리(EPT PDPTE)로 구성됩니다.EPT PDPTE는 다음과 같이 정의된 물리 주소를 사용하여 선택됩니다.- bits 63:52 는 모두 0입니다.

- bits 51:12 는

EPT PML4E에서 가져온 값 입니다. - bits 11:3은 게스트 물리 주소의 bits 38:30 입니다.

- bits 2:0 은 모두 0입니다.

EPT PDPTE 는 게스트 물리 주소의 bits 47:30 을 사용하여 식별되므로 게스트 물리 주소 공간의 1-GByte 영역에 대한 액세스를 제어합니다. EPT PDPTE 의 사용은 해당 엔트리에서 bit 7의 값에 의존합니다.

EPT PDPTE의 bit 7이 1인 경우,EPT PDPTE는1-GByte Page를 매핑합니다. 최종적으로 물리 주소는 아래와 같이 계산됩니다.- bits 63:52 는 모두 0입니다.

- bits 51:30 은

EPT PDPTE에서 가져온 값 입니다. - bits 29:0 은 원래 게스트 물리 주소에서 가져온 값입니다.

1-Gbyte 페이지를 매핑하는

EPT PDPTE의 포맷은 아래와 같습니다.

-

EPT PDPTE의 bit 7이 0인 경우, 4-Kbyte 로 자연스럽게 정렬된EPT Page-Directory는EPT PDPTE의 bits 51:12 에 지정된 물리 주소에 위치합니다.EPT Page-Directory를 참조하는EPT PDPTE의 포맷은 아래와 같습니다.

EPT Page-Directory는 512개의 64bits 로 이루어진 엔트리(PDE)로 구성됩니다.EPT PDE는 다음과 같이 정의된 물리 주소를 사용하여 선택됩니다.- bits 63:52 는 모두 0입니다.

- bits 51:12 는

EPT PDPTE에서 가져온 값 입니다. - bits 11:3 은 게스트 물리 주소의 bits 29:21 입니다.

- bits 2:0 은 모두 0입니다.

EPT PDE 는 게스트 물리 주소의 bits 47:21 을 사용하여 식별되기 때문에 게스트 물리 주소 공간의 2-Mbyte 영역에 대한 액세스를 제어합니다. EPT PDE 의 사용은 해당 엔트리에서 bit 7에 의존합니다.

EPT PDE의 bit 7이 1이면EPT PDE는 2-Mbyte 페이지를 매핑합니다. 최정적으로 물리 주소는 다음과 같이 계산됩니다.- bits 63:52 는 모두 0입니다.

- bits 51:21 은

EPT PDE에서 가져온 값 입니다. - bits 20:0은 원래 게스트 물리 주소의 비트 입니다.

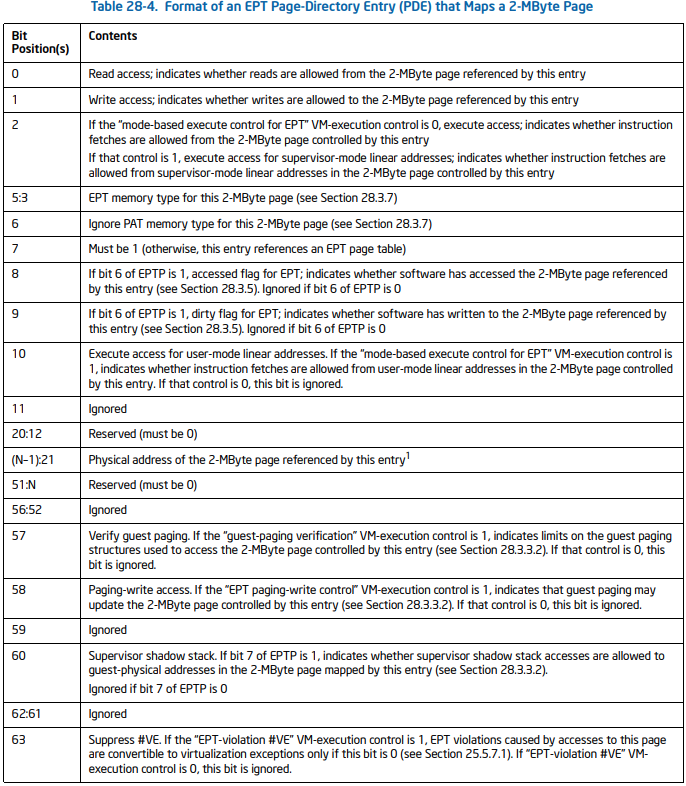

2-Mbyte 페이지를 매핑하는

EPT PDE의 형식은 아래와 같습니다.

-

EPT PDE의 bit 7이 0인 경우, 4-Kbyte 로 자연스럽게 정렬된EPT Page Table은EPT PDE의 bits 51:12 에 지정된 물리 주소에 위치합니다.EPT Page Table을 참조하는EPT PDE의 형식은 아래와 같습니다.

EPT Page Table은 512개의 64bits로 이루어진 엔트리(PTE)로 구성됩니다.EPT PTE는 아래와 같이 정의된 물리 주소를 사용하여 선택됩니다.- bits 63:52 는 모두 0입니다.

- bits 51:12 는

EPT PDE에서 가져온 값 입니다. - bits 11:3 은 게스트 물리 주소의 bits 20:12 입니다.

- bits 2:0 은 모두 0입니다.

EPT PTE는 게스트 물리 주소의 bits 47:12 를 사용하여 식별되므로 모든EPT PTE는 4-Kbyte 페이지로 매핑됩니다. 최종적으로 물리 주소는 다음과 같이 계산됩니다.- bits 63:52 는 모두 0입니다.

- bits 51:12 는

EPT PTE에서 가져온 값 입니다. - bits 11:0 은 원래 게스트 물리 주소의 비트입니다.

EPT PTE의 형식은 아래와 같습니다.

EPT Paging-Structure Entry 는 bits 2:0 중 하나가 1인 경우 존재(Present)합니다. 그렇지 않으면 해당 엔트리는 존재하지 않습니다(Not Present). 프로세서는 bits 62:3 을 무시하고 엔트리를 사용하여 다른 EPT Paging-Structure Entry 를 참조하거나 물리 주소를 생성하지 않습니다. EPT Paging-Structure 가 존재하지 않는 변환이 발생하는 게스트 물리 주소를 사용하는 참조는 EPT Violation 을 발생시킵니다.

위의 설명에서는 EPT Paging-Structure 가 서로를 참조하는 방법과 게스트 물리 주소를 변환할 때 논리 프로세서가 이러한 구조를 트레버스 하는 방법에 대해 설명했습니다.

변환 과정의 모든 세부 사항을 다루진 않았습니다. 추가 세부 정보는 아래와 같이 제공됩니다.

- 변환 프로세스가

VM Exit로 이루어질 수 있는 상황 EPT변환 메커니즘과 메모리 타이핑 간의 상호 작용

[-] EPT-Induced VM Exits

게스트 물리 주소를 사용하여 액세스하면 EPT Misconfiguration, EPT Violation, Page-Modification Log-Full Event 로 인해 VM Exit 가 발생할 수 있습니다.

EPT Misconfiguration은 게스트 물리 주소를 변환하는 과정에서 논리 프로세서가 지원되지 않는 값을 포함하는EPT Paging-Structure Entry를 발견하게 됐을 때 발생합니다.EPT Violation은EPT의 잘못된 구성은 없지만EPT Paging-Structure Entry가 게스트 물리 주소를 사용한 액세스를 허용하지 않을 때 발생합니다.Page-Modification Log-Full Event는 논리 프로세서가Page-Modification Log Entry를 생성해야 함을 판단했으나 현재 로그가 가득 찼을 때 발생합니다.

위와 같은 이벤트는 게스트 물리 주소를 사용하여 메모리에 액세스하려는 시도로 인해 발생합니다. MOV to CR3 명령을 사용하여 게스트 물리 주소를 CR3 에 로드하면 해당 주소가 페이징 구조에 액세스하는 데 사용될 때 까지 EPT Violation 이나 EPT Misconfiguration 이 발생하지 않을 수 있습니다.

Second_EPT-violation #VE 제어가 1인 경우 특정 EPT Violation 으로 인해 VM Exit 대신 가상화된 예외가 발생할 수 있습니다.

[+] EPT Misconfigurations

게스트 물리 주소의 변환에서 다음 조건 중 하나를 충족하는 EPT Paging-Structure Entry 가 발생하면 EPT 의 구성이 잘못된 것 입니다.

- 엔트리의 bit 0이 지워진 경우와 다음 중 하나로 유지됩니다.

- bit 1 이 설정된 경우(데이터 쓰기가 허용됨을 나타냄)

- 프로세서는 실행

execute-only변환을 지원하지 않으며 다음 중 하나가 유지됩니다.(VMM은IA32_VMX_EPT_VPID_CAP을 읽고execute-only변환이 지원되는지에 대한 여부를 확인해야 합니다.)- bit 2 가 설정된 경우(명령어 페칭이 허용됨을 나타냄, 실행의 허용)

Second_mode-based execute control for EPT제어가 1이고 bit 10이 1로 설정된 경우(유저모드 선형 주소에서의 실행이 허용됨을 나타냄)

Tertiary_EPT paging-write control제어가 1이고 엔트리는 페이지를 매핑하며 bit 58이 1로 설정된 경우(페이징 쓰기가 허용됨을 나타냄)

- 엔트리가 존재하고 다음 중 하나로 유지됩니다.

- 예약된 비트가 1로 설정되었습니다. 여기에는 논리 프로세서의 물리 주소 너비를 벗어나는 bits 51:12 범위의 비트 설정이 포함됩니다.

- 해당 엔트리는 게스트 물리 주소(bit 7이 1으로 설정된

EPT PDE또는EPT PTE)를 변환하는 데 사용되는 마지막 엔트리이며 bits 5:3(EPT memory type)의 값이 예약된 값 2, 3, 7 중 하나로 설정되었습니다.

[+] EPT Violation

EPT Violation 은 변환에서 EPT Misconfiguration 이 발생하지 않은 게스트 물리 주소를 사용하여 액세스하는 동안 발생할 수 있습니다.

아래의 설명에서 실행 방지의 경우, 명령어를 가져오지 못하는 경우를 의미합니다. 즉 명령어 페칭이 불가하기 때문에 실행이 불가하다는 의미로 이해하였습니다.

EPT Violation 은 아래의 경우에 발생합니다.

- 게스트 물리 주소의 변환에서 존재하지 않는

EPT Paging-Structure Entry를 발견한 경우. EPT Paging-Structure Entry에서 bit 0(read access) 이 0으로 설정되어 있을 때Read행위의 액세스가 발생한 경우.-

EPT Paging-Structure Entry에서 bit 1(write access) 이 0으로 설정되었 있을 때Write행위의 액세스가 발생한 경우. 액세스 및Dirty Flag를 업데이트하기 위한 쓰기 역시 데이터 쓰기로 간주됩니다.EPTP의 bit 6(EPT에 대한 액세스 및dirty flags활성화 여부)이 1인 경우 게스트 페이징 엔트리에 대한 프로세서 액세스는EPT Violation과 관련된 데이터 쓰기로 처리됩니다. 따라서 게스트Paging-Structure Entry의 게스트 물리 주소를 변환하는 데 사용되는EPT Paging-Structure Entry중 하나에서 bit 1 이 0으로 설정되면 해당 엔트리를 통해 선형 주소를 변환할 때EPT Violation이 발생합니다.액세스 및

dirty flag를 업데이트하기 위해 게스트 페이징 구조에 대한 프로세서 쓰기를paging write라고 합니다.Tertiary_EPT paging-write control제어가 1인 경우 페이지를 매핑하는EPT Paging-Structure Entry에서write access비트를 지우더라도 해당 항목의 bit 58(paging-write access)가 1이면paging write를 방지하지 않습니다.Second_sub-page write permission for EPT제어가 1이면EPT Violation을 유발할 수 있는 위와 같은 내용들의 경우에도 발생하지 않습니다. 게스트 물리 주소가 4-Kbyte 페이지를 사용하여 매핑되고 페이지 매핑에 사용되는EPT PTE의 bit 61(sub-page write permissions)이 1인 경우, 특정 128-bytesub-page에 쓰기가 허용될 수 있습니다. EPT Paging-Structure Entry에서 실행에 대한 액세스를 방지합니다. 이는Second_mode-based execute control for EPT제어의 설정에 따라 다릅니다.- 해당 제어가 0이고,

EPT Paging-Structure Entry에서 bit 2(execute access)가 0일 때Execute행위의 실행이 발생한 경우EPT Violation이 발생합니다. - 해당 제어가 1인 경우 다음 중 아래의 경우 실행이 방지됩니다.

-

Paging은 대상 바이트의 선형 주소를Supervisor-mode address로 매핑하고EPT Paging-Structure Entry의 bit 2(execute access for supervisor-mode linear addresses)가 0인 경우선형 주소 변환을 제어하는

Paging-Structure Entry중 하나에서 bit 2(U/S flag)가 0이면 페이징은 선형 주소를Supervisor-mode address로 매핑합니다. -

Paging은 대상 바이트의 선형 주소를User-mode address로 매핑하고EPT Paging-Structure Entry의 bit 10(execute access for user-mode linear addresses) 가 0인 경우선형 주소 변환을 제어하는

Paging-Structure Entry에서 bit 2(U/S flag)가 1이면 페이징은User-mode address로 매핑합니다. 페이징이 비활성화되면(CR0.PG = 0) 모든 선형 주소는User-mode address입니다.

-

- 해당 제어가 0이고,

EPTP의 bit 7(enable supervisor shadow-stack control)이 1로 설정된 경우, 액세스는Supervisor Shadow-Stack Access입니다. 아래 내용에 해당하는 경우EPT Paging-Structue Entry에서 해당 액세스가 허용되지 않습니다.- bit 0(

read access)가 0인 경우 - bit 1(

write access)이 0인 경우 - bit 60(

supervisor-shadow stack access)가 0인 경우

EPT Paging-Structure Entry의 bit 60(supervisor-shadow stack access)와EPTP의 bit 7(enable supervisor shadow-stack control)은 다른 액세스에는 영향을 주지 않습니다.- bit 0(

-

Tertiary_guest-paging verification,Tertiary_EPT paging-write control제어가 모두 1인 경우, 선형 주소 변환과 관련된 특정 액세스에 대해 게스트 페이징에 대한 검증이 수행됩니다.특히, 게스트 페이징 검증은 선형 주소에 대한 페이지를 매핑하는 게스트

Paging-Structure Entry에 게스트 물리 주소를 사용하는 특정 액세스에 적용될 수 있습니다. 해당 게스트 물리 주소에 대한 페이지를 매핑하는EPT Paging-Structure Entry의 bit 57(verify guest paging)이 1으로 설정된 경우 적용됩니다.게스트 페이징 검증이 발생할 때 원래 선형 주소를 변환하는 중 사용된 게스트

Paging-Structure Entry의EPT Paging-Structure Entry내 bit 58(paging-write access)가 0으로 설정된 경우EPT Violation이 발생합니다.

[+] Prioritization of EPT Misconfiguration and EPT Violations

선형 주소를 물리 주소로 변환하려면 EPT 를 사용하여 게스트 물리 주소를 하나 이상 변환해야 합니다.

이 섹션에서는 선형 주소를 사용하여 메모리에 액세스할 때 발생할 수 있는 여러가지 이벤트에 대해 EPT 로 인한 VM Exit 가 발생하는 것의 상대적 우선 순위가 지정되는 내용에 대해 설명합니다.

게스트 물리 주소에 액세스하는 경우, EPT Misconfiguration 또는 EPT Violation 이 발생하는지 여부는 아래와 같은 반복 프로세스(Iterative Process)를 기반으로 결정됩니다.

EPT Translation Mechanism 을 단순화 한 내용입니다. 1단계, 2단계 실행의 경우 해당 엔트리에서 최종 물리 주소가 결정나는지에 대한 단계입니다.EPT Paging-Structure Entry를 읽습니다.(최초EPT PML4E)- 엔트리가 존재하지 않으면

EPT Violation이 발생합니다. - 엔트리가 존재하지만 내용이 제대로 구성되지 않은 경우

EPT Misconfiguration이 발생합니다. - 엔트리가 존재하고 적절하게 구성된 경우, 엔트리는 다른

EPT Paging Structure를 참조하는지에 대한 여부(bit 7이 1로 설정된EPT PDE인지 또는EPT PTE인지)에 따라 달라집니다.- 엔트리가 다른

EPT Paging Structure를 참조하는 경우 해당 구조의 엔트리에 액세스합니다. 해당 엔트리에 대해 1단계가 실행됩니다. - 아닌 경우 최종 물리 주소(기존의 게스트 물리 주소 변환)를 생성하는 데 사용됩니다. 2단계가 실행됩니다.

- 엔트리가 다른

- 엔트리가 존재하지 않으면

- 최종 물리 주소가 결정되면

EPT Paging-Structure Entry에 의해 결정된 권한이 평가됩니다.- 게스트 물리 주소에 대한 액세스가 허용되지 않은 경우

EPT Violation이 발생합니다. - 게스트 물리 주소에 대한 액세스가 허용되는 경우 최종 물리 주소를 이용하여 메모리에 액세스합니다.

- 게스트 물리 주소에 대한 액세스가 허용되지 않은 경우

CR0.PG = 1 인 경우, 선형 주소 변환도 반복 프로세스입니다. 각 게스트의 물리 주소는 자체적으로 EPT 를 사용하여 변환되며 EPT 로 인해 VM Exit 가 발생할 수 있습니다.(EPT-induced VM Exit)

다음 내용에서는 이러한 반복 프로세스 중에 Page-Fault 및 EPT-induced VM Exit 를 인식하는 방법에 대해 자세히 설명합니다.

- 게스트 물리 주소(최초

CR3의 주소)를 이용하여 게스트Paging-Structure Entry에 액세스하려고 시도합니다.EPT Misconfiguration또는EPT Violation이 발생하여 액세스가 실패하면EPT-induced VM Exit가 발생합니다.- 액세스로 인해

EPT-induced VM Exit가 발생하지 않으면 변환이 계속됩니다. 게스트 페이징 검증(guest-paging verification)이 활성화된 경우 프로세서는EPT Paging-Structure Entry이 게스트 물리 주소에 대한 페이지를 매핑하는데 bit 58(paging write)가 설정되었는지에 대한 여부를 기록합니다. 그런 다음 게스트Paging-Structure Entry의 bit 0(the present flag)을 참조합니다.- bit 0(

the present flag)가 0이거나 예약된 비트가 설정된 경우Page Fault가 발생합니다. - bit 0이 1이면 예약된 비트가 설정되지 않고 엔트리가 다른 게스트

Paging-Structure를 참조하는지 여부(PS = 1인 게스트PDE또는 게스트PTE)에 따라 달라집니다.- 엔트리가 다른 게스트

Paging-Structure를 참조하는 경우 해당 구조의 엔트리에 액세스합니다. 해당 엔트리에 대해 1단계가 실행됩니다. - 그렇지 않으면 엔트리는 최종 게스트 물리 주소(기존 선형 주소의 변환)을 생성하는 데 사용합니다. 2단계가 실행됩니다.

- 엔트리가 다른 게스트

- bit 0(

- 최종 게스트 물리 주소가 결정되면 게스트

Paging-Structure Entry에 의해 결정된 권한이 평가됩니다.- 해당 권한으로 인해 선형 주소에 대해 액세스가 허용되지 않는 경우

Page Fault가 발생합니다. - 선형 주소에 대해 액세스가 허용되면 최종 게스트 물리 주소에서 메모리에 액세스를 시도합니다.

EPT Misconfiguration또는EPT Violation으로 인해 액세스가 실패하면EPT-induced VM Exit가 발생합니다. 이 시점에 위의 1.b에 작성된paging-wrtie비트를 이용하여 게스트 페이징 검증이 발생합니다.- 오류가 발생하지 않으면 최종 물리 주소(

EPT를 사용하여 최종 게스트 물리 주소로 변환 된)를 사용하여 메모리에 액세스합니다.

- 해당 권한으로 인해 선형 주소에 대해 액세스가 허용되지 않는 경우

CR0.PG = 0 인 경우 선형 주소는 게스트 물리 주소로 처리되고 EPT를 사용하여 변환됩니다. 이 프로세스가 EPT Violation 이나 EPT Misconfiguration 이 발생하지 않으면 물리 주소를 생성하고 EPT Paging-Structure Entry 가 허용하는 권한을 결정합니다.

이러한 권한이 물리 주소에 대한 액세스를 허용하지 않으면 EPT Violation 이 발생하고, 그렇지 않으면 물리 주소를 이용하여 메모리에 액세스하게 됩니다.

[-] Sub-Page Write Permissions

위에서 EPT 가 EPT Violation 을 이용하여 게스트 물리 주소에 대한 액세스 권한을 적용하는 방법에 대해 설명했습니다.

이러한 액세스 권한은 게스트 물리 주소를 변환하는 데 사용되는 EPT Paging-Structure Entry 를 이용하여 결정되기 때문에 세부 수준은 페이지를 매핑하는 데 사용되는 것으로 제한됩니다.(1-GByte, 2-MByte, 4-KByte)

Sub-Page Write Permission 기능을 사용하면 게스트 물리 주소에 대한 Write 액세스를 좀 더 세밀하게 제어할 수 있습니다. 또한 자연스럽게 정렬된 128 바이트 단위의 Sub-Page 로 Write 액세스를 제어할 수 있습니다.

특히 이 기능을 사용하면 Write 가 불가능한 4-KByte의 Selected Sub-Page 에 쓰기가 가능합니다.

Second_sub-page write permissions for EPT 제어가 1인 경우 Sub-Page Write Permission 이 활성화됩니다.

[+] Write Accesses That Are Eligible for Sub-Page Write Permissions

게스트 물리 주소는 EPT Paging-Structure Entry 내 bit 1(write access)이 0으로 설정되어 write 액세스가 허용되지 않는 경우 sub-page write permission 에 적합(Eligible)합니다.

위의 내용과 다른 이유로 허용되지 않는 경우(ex. 변환 중 존재하지 않는 EPT Paging-Structure Entry 를 발견), sub-page write permission 에 부적합 합니다.

또한 게스트 물리 주소는 4-Kbyte 페이지를 사용하여 매핑되고 페이지 매핑에 사용되는 EPT PTE 의 bit 61(sub-page write permissions)이 1인 경우에만 사용할 수 있습니다.(더 큰 페이지에 매핑된 게스트 물리 주소는 적합하지 않습니다.)

일부 메모리 액세스의 경우 프로세서는 EPT PTE 의 bit 61의 설정 여부와 관계없이 sub-page write permission 을 적용하지 않습니다. 이러한 경우는 아래와 같습니다.

- 트랜잭션 영역 내에서 수행되는

write액세스 Enclave의ELRANGE내의 주소에 대한write액세스Intel SGX명령어에 의한EPC(Enclave Page Cache)에 대한write액세스accessed flag또는dirty flag를 업데이트하는 게스트Paging-Structure Entry에 대한write액세스- 액세스 시 게스트

Paging-Structure Entry에 대한 프로세서 액세스 및EPT에 대한dirty flag가 활성화 된 경우 - 두 개의 4-KByte 페이지를 가로지르는

write액세스, 이 경우 둘 다 적용되지 않거나 하나의 페이지에만 적용될 수 있습니다.(가로지른다는 표현은 연속되는 페이지를 의미하는 것인지 동시성을 의미하는지 의문입니다.) - 다중

write액세스를 수행하는 명령에 의한 쓰기(sub-page write permission은 주로AND, MOV, OR, TEST, XCHG, XOR와 같은 기본 명령을 위한 것 입니다.)

게스트 물리 주소가 Sub-Page Write Permission 에 적합한 경우 아래에서 설명하게 될 프로세스를 통해 주소에 대한 write 를 허용할지 여부를 결정합니다.

[+] Determining and Access’s Sub-Page Write Permission

Sub-Page Write Permission 은 4-KByte 의 128-Byte Sub-Page(이하 “하위 페이지”) 32개에 대해 각각 write 액세스를 개별적으로 제어합니다. 게스트 물리 주소의 bits 11:7 은 하위 페이지를 식별합니다.

sub-page write permission 에 적합한 각 게스트 물리 주소에는 64bit의 Sub-Page Permission Vector(SPP Vector)가 있습니다. 4-KByte 페이지의 모든 주소는 동일한 SPP Vector 를 사용합니다.

주소의 하위 페이지 번호(bits 11:7)가 S인 경우, Sub-Page Write Permission 의 비트 2S가 1로 설정된 경우에만 쓰기가 허용됩니다.(SPP 에서 홀수 위치에 있는 비트는 사용되지 않으며 0이어야 합니다.)

각 페이지의 SPP Vector 는 메모리에 위치합니다. Sub-Page Write Permission 에 적합한 게스트 물리 주소에 대해 write 액세스인 경우 프로세서는 다음 프로세스를 통해 주소의 SPP Vector 를 찾습니다.

VM-execution control field내SPPTP(Sub-Page-Permission-Table-Pointer)는 4-KByte 의SPP Table(SPPL4 table)의 물리 주소를 포함합니다. 게스트 물리 주소의 bits 47:39는SPPL4E라고 하는 해당 테이블의 64bit 크기의 엔트리를 식별합니다.- 4-KByte

SPPL3 table은 선택한SPPL4E의 물리 주소에 위치합니다. 게스트 물리 주소의 bits 38:30 은SPPL3E라고 하는 해당 테이블의 64bit 크기의 엔트리를 식별합니다. - 4-KByte

SPPL2 table은 선택한SPPL3E의 물리 주소에 위치합니다. 게스트 물리 주소의 bits 29:21은SPPL2E라고 하는 해당 테이블의 64bit 크기의 엔트리를 식별합니다. - 4-KByte

SPP-vector table, SPPL1 table은 선택한SPPL2E의 물리 주소에 위치합니다. 게스트 물리 주소의 bits 20:12는 64 bit 크기의SPP Vector를 식별합니다. 벡터의 bit 2S는 주소가 기록될 수 있는지 여부를 결정합니다.

단일 4-KByte 페이지의 여러 128-Byte 하위 페이지에 대한 write 액세스는 각 하위 페이지의 SPP Vector 가 표시된 비트가 1로 설정된 경우에만 허용됩니다.

다음 내용은 2개의 4-KByte 페이지에 쓰는 경우에 적용됩니다.

- 두 페이지 모두

write가 허용되지 않을 경우, 해당 페이지의 게스트 물리 주소가Sub-Page Write Permission에 적합하더라도 액세스가 허용되지 않을 수 있습니다.

각 엔트리(SPPL4E, SPPL3E, SPPL2E)의 bit 0 은 Valid 를 의미합니다. 위의 프로세스에서 bit 0인 엔트리에 액세스하면 중지되고 논리 프로세서에서 SPP Miss 가 발생합니다.

각 엔트리(SPPL4E, SPPL3E, SPPL2E)의 bits 11:1, bits 63:N 은 예약된 비트입니다. 위의 프로세스에서 bit 0(Valid)가 1이고 일부 예약 비트가 설정된 엔트리에 액세스하면 프로세스가 중지되고 논리 프로세서에서 SPP Misconfiguration 이 발생합니다.

이렇게 발생한 SPP Miss, SPP Misconfiguration 은 SPP-related events 라고 부르며, VM Exit 가 발생합니다.

[-] Accessed and Dirty Flags for EPT

Intel 64 아키텍처는 일반적인 Paging-Structure Entry 에서 Accessed, Dirty flag 를 지원합니다. 일부 프로세서는 EPT Paging-Structure Entry 에서 동일한 플래그가 지원됩니다. VMM 은 프로세서가 이 기능을 지원하는지에 대한 여부를 결정하기 위해 MSR IA32_VMX_EPT_VPID_CAP 을 읽어 참조해야 합니다.

VMM 은 VM-exeucution control field 내 EPTP(Extended-Page-Table-Pointer)의 bit 6을 이용하여 EPT 에 대한 accessed, dirty flag 를 활성화할 수 있습니다. 이 비트가 1이면 프로세서는 아래 설명된대로 EPT 에 대한 accessed and dirty flag 를 설정합니다.

또한 이 플래그를 설정하면 게스트 Paging-Structure Entry 에 대한 프로세서 액세스가 write 로 처리됩니다.

게스트 물리 주소 변환 중에 사용되는 모든 EPT Paging-Structure Entry 의 경우 bit 8이 Accessed Flag 입니다. 페이지를 매핑하는 EPT Paging-Structure Entry 의 경우(구조를 참조하는 것 외에) bit 9는 Dirty Flag 입니다.

프로세서는 게스트 물리 주소 변환의 일부로 EPT Paging-Structure Entry 를 사용할 때 마다 해당 엔트리에 accessed flag 를 설정합니다.(설정되지 않은 경우)

게스트 물리 주소에 write 가 발생할 때 마다 프로세서는 게스트 물리 주소에 대한 최종 물리 주소(EPT PTE 또는 bit 7이 1인 EPT Paging-Structure Entry)를 식별하는 EPT Paging-Structure Entry 에 Dirty Flag 를 설정합니다.(설정되지 않은 경우)

EPT 에 대한 Accessed, Dirty Flag 가 활성화된 경우 게스트 Paging-Structure Entry 에 대한 프로세서 액세스가 쓰기로 처리됩니다. 따라서 이러한 액세스는 프로세서가 게스트 Paging-Structure Entry 의 최종 물리 주소를 식별하는 EPT Paging-Structure Entry 의 Dirty Flag 를 설정하게 합니다.

이러한 플래그는 고정(”Sticky”)되어 있으며, 이는 일단 설정되면 프로세서가 플래그를 지우지 않음을 의미합니다. VMM 만이 이를 지울 수 있습니다.

프로세서는 EPT Paging-Structure Entry의 정보를 TLB 및 Paging-Structure Cache에 캐시할 수 있습니다. 이 의미는 VMM 이 Accessed 또는 Dirty flag를 1에서 0으로 변경할 경우 프로세서가 영향을 받는 게스트 물리 주소를 사용하여 후속 액세스에서 메모리에 해당 비트를 설정하지 않을 수 있음을 의미합니다.

[-] Page-Modification Logging

참고 : 링크

EPT 에 대한 Accessed, Dirty Flag 가 활성화되면 VMM 은 Page-Modification Logging, PML 이라는 기능을 이용하여 게스트 물리 주소에 대한 Write 를 추적할 수 있습니다.

VMM 은 VM-execution control 내 enable PML 제어를 1으로 설정함으로써 page-modification logging 을 활성화할 수 있습니다. 활성화되면 프로세서는 아래에 설명된 대로 page-modificaiton log 에 엔트리를 추가합니다.

page-modification log 는 VM-execution control field 내 PML address 의 물리 주소에 위치한 4-KByte 메모리 영역입니다.

Page-Modificaiton Log 는 64bit 로 이루어진 엔트리 512개로 구성되어 있습니다. VM-execution control field 내 PML index 는 사용할 다음 엔트리를 나타냅니다.

게스트 물리 액세스를 허용하기 전에 프로세서는 EPT에 대한 accessed, dirty flag 를 설정해야 하는지 결정할 수 있습니다. 이 경우 프로세서는 PML Index 를 검사합니다.

PML Index 가 0-511 범위에 있지 않으면 Page-Modification Log-Full Event 가 발생하고 VM Exit 가 발생합니다.

범위 안에 있는 경우 프로세서는 EPT 에 대한 accessed, dirty flag 를 업데이트 합니다. 프로세서가 EPT 에 대해 dirty flag 를 업데이트 한 경우(0→1) 다음과 같이 동작합니다.

- 액세스 게스트 물리 주소는

page-modification log에 기록됩니다. 구체적으로 게스트 물리 주소는PML Address에PML Index의 8배를 추가하여 결정된 물리 주소에 기록됩니다. 기록된 값의 bits 11:0은 항상 0 입니다. PML Index는 1씩 감소합니다. 이로 인해 값이 0에서 FFFFh 로 전환될 수 있습니다.

만일 감소하다 FFFFh가 되는 경우 프로세서는 PML Index 값이 0-511 범위에 있지 않다고 판단하여 Page-Modification Log-Full Event 를 생성하며 이 시점에서 더 이상의 로깅은 발생하지 않습니다.

[-] EPT and Memory Typing

논리 프로세서에서 EPT 가 사용되는 동안 메모리 액세스에 대한 메모리 유형 사용을 결정하는 방법을 설명합니다.

[+] Memory Type Used for Accessing EPT Paging Structures

EPT Paging-Structure 에 대한 액세스를 위해 메모리 유형이 어떻게 결정되는지 설명합니다. 결정은 먼저 CR0의 bit 30(cache disable-CD) 값을 기반으로 합니다.

CR0.CD = 0인 경우 이러한 참조에 사용되는 메모리 유형은VM-execution control field내EPTP의 bits 2:0 에 의해 지정됩니다. 값이 0이면uncacheable type(UC)이고 6이면write-back type(WB)를 나타냅니다.CR0.CD = 1인 경우 이러한 참조에 사용되는 메모리 유형은uncacheable type(UC)입니다.

[+] Memory Type Used for Translated Guest-Physical Addresses

게스트 물리 주소를 이용하는 메모리 액세스의 Effective Memory Type(EPT 를 이용하여 변환된 액세스)은 메모리에 액세스하는 데 사용되는 메모리 유형입니다.(이하 “유효 메모리 유형”)

유효 메모리 유형은 CR0.CD 의 값 또는 게스트 물리 주소를 변환하는 데 사용되는 마지막 EPT Paging-Structure Entry 및 PAT 메모리 유형을 기반으로 합니다.

PAT Memory Type은CR0.PG값에 따라 다릅니다.CR0.PG = 0이면PAT Memory Type은WB입니다.CR0.PG = 1이면PAT Memory Type은IA32_PAT MSR에 의해 선택된 메모리 유형입니다.

EPT Memory Type은 마지막EPT Paging-Structure Entry의 bits 5:3 에 지정됩니다.- 0 = UC, 1= WC, 4 = WT, 5 = WP, 6 = WB 를 의미하며 다른 값은 예약되어 있으며 설정되는 경우

EPT Misconfiguration이 발생합니다.

- 0 = UC, 1= WC, 4 = WT, 5 = WP, 6 = WB 를 의미하며 다른 값은 예약되어 있으며 설정되는 경우

CR0.CD = 0이면 유효 메모리 유형은 마지막EPT Paging-Structure Entry의 bit 6에 따라 다릅니다.-

값이 0이면 유효 메모리 유형은

MTRR Memory Type대신EPT Memory Type을 이용하여 지정된EPT Memory Type과PAT Memory Type의 조합입니다.

-

값이 1이면 유효 메모리 유형은

EPT Memory Type입니다.PAT Memory Type은 무시됩니다.

-

CR0.CD = 1인 경우 유효 메모리 유형은uncacheable(UC)입니다.

MTRR 은 게스트 물리 주소에 액세스하는 데 사용되는 메모리 유형에 영향을 주지 않습니다.

[0x04] Caching Translation Information

메모리 구조의 프로세서 데이터를 캐싱하여 주소 변환 프로세스를 가속화할 수 있습니다. 이러한 캐싱은 추후에 설명하게 될 기본적인 페이징에 대한 내용을 다룰 때 상세하게 다룰 예정입니다.

현재 파트에서는 이 캐싱이 VMX 아키텍처와 상호작용하는 방식을 설명합니다.

VMX Operation을 위한 아키텍처의 VPID, EPT 기능은 이 캐싱 아키텍처를 확장합니다. EPT 는 게스트 물리 주소 공간을 정의하고 선형 주소 공간과 물리 주소 공간으로의 변환을 정의합니다.

두 기능 모두 논리 프로세서가 페이징 구조에 캐시된 정보를 만들고 사용할 수 있는 방법을 제어합니다.

[-] Information That May Be Cached

추후에 게시 될 페이징과 관련된 내용 중 Caching Translation Information 은 논리 프로세서에 의해 캐싱될 수 있는 두 종류의 변환 관련 정보를 식별합니다.

Linear Page Number 에서 Physical Page Frame 으로 매핑하는 Translation 과 Linear Page Number 의 상위 비트를 해당 상위 비트와 일치하는 선형 주소를 변환하는 데 사용되는 Paging-Structure Entry 에 매핑하는 Paging-Structure Cache 입니다.

VPID 및 EPT 가 사용 중일 때 동일한 종류의 정보가 캐시될 수 있습니다. 논리 프로세서는 기능에 따라 이러한 정보를 캐싱하고 사용할 수 있습니다. 기능이 다른 정보는 아래와 같이 식별됩니다.

Linear Mapggins의 경우 두 종류가 있습니다.Linear Translation, 이들 각각은 액세스 권한 및 메모리 유형에 대한 정보와 함께Linear Page Number에서 변환되는Physical Page Frame으로의 매핑입니다.Linear Paging-Structure-Cache Entries, 이들 각각은 액세스 권한에 대한 정보와 함께 선형 주소의 해당 영역을 변환하는 데 사용되는 페이징 구조의 물리 주소에 대해 선형 주소의 상위 부분에서 매핑됩니다. 예를 들어 선형 주소의 bits 47:39 는 관련Page-Directory-Pointer Table주소에 매핑됩니다.

선형 매핑에는

EPT Paging-Structure의 정보가 포함되어 있지 않습니다.Guest-Physical Mapping의 경우 두 종류가 있습니다.Guest-Physical Translation, 이들 각각은 액세스 권한 및 메모리 유형에 대한 정보와 함께Guest-Physical Page Number에서 변환되는Physical Page Frame으로의 매핑입니다.Guest-Physical Paging-Structure-Cache Entries, 이들 각각은 액세스 권한에 대한 정보와 함께Guest-Physical Address의 해당 영역을 변환하는 데 사용되는EPT Paging-Structure의 물리 주소로의 매핑입니다.

액세스 권한 및 메모리 유형에 대한 게스트 물리 매핑 정보는

EPT Paging-Structure에서 파생됩니다.Combined Mappings의 경우 두 가지 종류가 있습니다.Combined Translation, 이들 각각은 액세스 권한 및 메모리 유형에 대한 정보와 함께Linear Page Number에서 변환되는Physical Page Frame으로의 매핑입니다.Combined Paging-Structure Cache Entries, 이들 각각은 액세스 권한에 대한 정보와 함께 선형 주소의 해당 영역을 변환하는 데 사용되는 페이징 구조의 물리 주소에 대해 선형 주소의 상위 부분에서 매핑됩니다.

액세스 권한 및 메모리 유형에 대한 결합(

combined)된 매핑의 정보는 게스트 페이징 구조와EPT페이징 구조 모두에서 파생됩니다.

[-] Creating And Using Cached Translation Information

- 아래 내용은

EPT가 사용되지 않는 동안 매핑 생성에 대한 설명입니다.(VMX non-root operation제외 포함)Linear Mapping을 생성할 수 있습니다.CR3의 현재 값에 의해 참조되는(직,간접적으로) 페이징 구조에서 파생되며 현재VPID및 현재PCID와 연결됩니다.- 존재하지 않거나(bit 0 = 0) 예약된 비트를 설정하는

Paging-Structure Entry에서 파생된 정보는Linear Mapping이 생성되지 않습니다. 예를 들어PTE가 없으면 변환에서 해당PTE를 사용하는 모든Linear Page Number에 대해Linear Mapping이 생성되지 않습니다. EPT를 사용하지 않는 동안에는Guest-Physical Mapping,Combined Mapping이 생성되지 않습니다.

- 아래 내용은

EPT를 사용하는 동안 매핑 생성에 대한 설명입니다.-

Guest-Physical Mapping을 생성할 수 있습니다. 현재EPTP의 bits 51:12 에 의해 참조되는(직,간접적으로)EPT페이징 구조에서 파생됩니다. 이 40 bits 에는EPT-PML4-Table이 포함됩니다.(EP4TA는 해당 40 비트를 나타냄)새로 생성된

Guest-Physical Mapping은 현재EP4TA와 연결됩니다. Combined Mapping을 생성할 수 있습니다. 현재EP4TA에 의해 참조되는(직접적으로)EPT페이징 구조에서 파생됩니다.CR0.PG = 1이면CR3의 현재 값에 의해 참조되는(직,간접적으로) 페이징 구조에서도 파생됩니다. 현재VPID, 현재PCID, 현재EP4TA와 연결됩니다.CR0.PG = 0인 경우Combined Paging-Structure Cache Enries가 생성되지 않습니다.- 존재하지 않거나 잘못 구성된

EPT Paging-Structure Entry에서 파생된 정보로Guest-Physical Mapping또는Combined Mapping이 생성되지 않습니다. - 존재하지 않거나 예약된 비트를 설정하는 게스트

Paging-Structure Entry에서 파생된 정보로Combined Mapping이 생성되지 않습니다. EPT를 사용하는 동안Linear Mapping은 생성되지 않습니다.

-

다음 내용은 다양한 매핑의 사용에 대해 자세히 설명합니다.

EPT가 사용되지 않는 경우(ex.VMX non-root operation이 아닌 경우) 논리 프로세서는 다음과 같이 캐시된 매핑을 사용할 수 있습니다.- 선형 주소를 사용하는 액세스의 경우 현재

VPID, 현재PCID와 연관된Linear Mapping을 사용할 수 있습니다. 또한 현재VPID, PCID와 연관된 전역TLB Entry를 사용할 수 있습니다. EPT가 사용되지 않는 동안Guest-Physical, Combined Mapping은 사용할 수 없습니다.

- 선형 주소를 사용하는 액세스의 경우 현재

EPT가 사용되는 경우 다음과 같이 캐시된 매핑을 사용할 수 있습니다.- 선형 주소를 사용하는 액세스의 경우 현재

VPID, PCID, EP4TA와 연관된Combined Mapping을 사용할 수 있습니다. 또한 현재VPID, EP4TA와 모든PCID와 연관된 전역TLB Entry를 사용할 수 있습니다. - 게스트 물리 주소를 사용하는 액세스의 경우 현재

EP4TA와 연결된Guest-Physical Mapping을 사용할 수 있습니다. EPT가 사용되는 동안Linear Mapping은 사용할 수 없습니다.

- 선형 주소를 사용하는 액세스의 경우 현재

[-] Invalidating Cached Translation Information

페이징 구조(EPT Paging-Structure, SPP Vector 를 찾는 데 사용되는 데이터 구조 포함)의 수정으로 인한 해당 구조와 논리 프로세서에 의해 캐시된 매핑 간 불일치가 발생할 수 있습니다.

특정 작업은 논리 프로세서에 의해 캐시된 정보를 무효화하고 이러한 불일치를 제거하는 데 사용할 수 있습니다.

[+] Operations that Invalidate Cached Mappings

아래와 같은 행위가 발생하는 경우 캐시된 매핑을 무효화합니다.

-

VMX Operation과 독립적TLB또는Paging-Structure Cache를 구조적으로 무효화하는 작업(ex.INVLPG, INVPCID명령)은LInear Mapping및Combined Mapping을 무효화합니다.현재

VPID에 대해서만 수행해야 합니다.(단,Combined Mapping의 경우 모든EP4TA에 대해 수행) 현재VPID에 대한Linear Mapping은EPT가 사용 중인 경우에도 무효화됩니다.EPT를 사용하지 않는 경우에도 현재VPID에 대한Combined Mapping이 무효화 됩니다. EPT Violation은 발생시킨 게스트 물리 주소를 변환하는 데 사용되는 모든Guest-Physical Mapping(현재EP4TA와 연관된)을 무효화합니다. 해당 게스트 물리 주소가 선형 주소의 변환인 경우EPT Violation은 현재PCID, VPID, EP4TA와 연결된 해당 선형 주소에 대한Combined Mapping도 무효화 합니다.VM-execution control내enable VPID제어가 0인 경우,VM Entry,VM Exit는VPID = 0000h(모든PCID)와 관련된Linear Mapping,Combined Mapping을 무효화 합니다.VPID 0000h에 대한Combined Mapping은 모든EP4TA에 대해 무효화 합니다.INVVPID명령을 실행하면Linear Mapping,Combined Mapping이 무효화 됩니다. 무효화는INVVPID Type, Descriptor라고 하는 명령어의 피연산자를 기반으로 합니다. 4개의INVVPID Type이 현재 정의되어 있습니다.Individual-Address:INVVPID Type이 0인 경우 논리 프로세서는INVVPID Descriptor에 지정된VPID와 연관되고 선형 주소를 변환하는 데 사용되는Linear Mapping,Combined Mapping을 무효화합니다.Single-Context:INVVPID Type이 1인 경우 논리 프로세서는INVVPID Descriptor에 지정된VPID와 연관된 모든Linear, Combined Mapping을 무효화합니다.All-Context:INVVPID Type이 2인 경우 논리 프로세서는VPID 0000h, 모든PCID를 제외하고 모든VPID와 연관된Linear, Combined Mapping을 무효화합니다.Single-Context-Retaining-Globals:INVVPID Type이 3인 경우 논리 프로세서는INVVPID Descriptor에 지정된VPID와 연관된Linear, Combined Mapping을 무효화 합니다.

INVEPT명령을 실행하면Guest-Physical, Combined Mapping이 무효화 됩니다. 무효화는INVEPT Type, Descriptor라고 하는 명령어의 피연산자를 기반으로 합니다. 두 가지의 유형이 정의되어 있습니다.Single-Context:INVEPT Type이 1이면 논리 프로세서는INVEPT Descriptor에 지정된EP4TA와 연관된 모든Guest-Physical, Combined Mapping을 무효화 합니다.All-Context:INVEPT Type이 2이면 논리 프로세서는INVEPT Descriptor에 지정된 모든EP4TA와 연관된Guest-Physical, Combined Mapping을 무효화합니다.

[+] Operations that Need Not Invalidate Cached Mappings

다음 항목에서는 캐시된 특정 매핑을 무효화하는데 필요하지 않은 작업에 대해 설명합니다.

VMX Operation과 무관하게TLB또는Paging-Structure Cache Entries를 구조적으로 무효화하는 작업은Guest-Physical Mapping을 무효화하는 데 필요하지 않습니다.INVVPID명령은Guest-Physical Mapping을 무효화하는 데 필요하지 않습니다.INVEPT명령은Linear Mapping을 무효화하는 데 필요하지 않습니다.Guest-Physical Mapping을 무효화하기 위해VMX Transition이 필요하지 않습니다.VM-execution control내enable VPID제어가 1이면Linear, Combined Mapping을 무효화하기 위해VMX Transition이 필요하지 않습니다.Linear, Guest-Physical, Combined Mapping을 무효화하는 데VMXON, VMXOFF명령이 필요하지 않습니다.

논리 프로세서는 언제든지 캐시된 매핑을 무효화할 수 있습니다. 이러한 이유로 위에서 식별된 작업은 반드시 필요하지 않음에도 지정된 매핑을 무효화할 수 있습니다.

[+] Guidelines for Use of the INVVPID Instruction

VMM 이 INVVPID 명령어를 사용해야 하는지 여부는 해당 VMM 이 메모리를 가상화하는 방법에 따라 다릅니다.

EPT 를 사용하지 않는 경우 VMM 이 게스트 페이징 구조를 가상화 중일 수 있습니다. 이러한 VMM 은 TLB 및 Paging-Structure Cache Entries 를 무효화하는 모든 작업 또는 일부 작업이 VM Exit 를 발생하도록 VMCS 를 구성할 수 있습니다.

VMM 이 이러한 작업을 에뮬레이트하는 경우 INVVPID 명령을 사용하여 논리 프로세서의 TLB 및 Paging-Structure Cache 가 적절하게 무효화되었는지 확인해야 할 수 있습니다.

VMM 이 INVVPID 명령을 사용해야 하는 경우에 대한 요구 사항은 Page-Table Virtualization 에 사용되는 특정 알고리즘에 따라 다릅니다.

INVLPG명령어를 에뮬레이션하려면 다음과 같이INVVPID명령을 실행해야 할 수 있습니다.INVVPID Type은 0이어야 합니다.(Individual-Address)INVVPID Descriptor의VPID는 실행이 에뮬레이트되는 가상 프로세서에 할당된 것이어야 합니다.INVVPID Descriptor의 선형 주소는 에뮬레이트되는INVLPG명령의 피연산자 주소입니다.

- 일부 명령은 전역 변환을 제외하고

TLB및Paging-Structure Cache의 모든 엔트리를 무효화합니다.MOV to CR3를 예로 들 수 있습니다.INVVPID Type은 3이어야 합니다.(Single-Context-Retaining-Globals)INVVPID Decriptor의VPID는 실행이 에뮬레이트되는 가상 프로세서에 할당된 것이어야 합니다.

- 일부 명령은 전역 변환을 포함하여

TLB및Paging-Structure Cache의 모든 엔트리를 무효화합니다.CR4.PGE의 값을 변경하게 하는MOV to CR4가 이러한 예시 입니다.INVVPID Type은 1이어야 합니다.(Single-Context)INVVPID Descriptor의VPID는 실행이 에뮬레이트되는 가상 프로세서에 할당된 것이어야 합니다.

EPT 를 사용하지 않는 경우 논리 프로세서는 생성하는 모든 매핑을 현재 VPID 와 연결하고 이러한 매핑을 사용하여 선형 주소를 변환합니다. 따라서 VMM 은 다른 페이지 테이블을 사용하는 다른 non-EPT 게스트에 대해 동일한 VPID 를 사용하면 안됩니다. 이렇게 되면 한 게스트가 다른 게스트와 연관된 변환을 사용하게 될 수 있습니다.

EPT 가 사용 중인 경우 위에 열거된 지침으로 인해 VM Exit 발생하지 않도록 VMCS 를 구성할 수 있으며, VMM 이를 에뮬레이트하지 않을 수 있습니다. 이 경우 게스트 소프트웨어에 의한 명령 실행은 TLB 및 Paging-Structure Cache 의 필수 항목을 적절하게 무효화합니다. INVVPID 명령이 필요하지 않습니다.

EPT 가 사용 중인 경우 논리 프로세서는 생성하는 모든 매핑을 현재 EPTP 의 bits 51:12 값과 연결합니다. VMM 이 게스트 마다 다른 EPTP 를 사용하는 경우 동일한 VPID 를 사용할 수 있습니다.

[+] Guidelines for Use of the INVEPT Instruction

아래에서는 INVEPT 명령을 이용하여 EPT 페이징 구조에서 캐시된 정보를 무효화하기 위한 지침을 제공합니다.

VMM은EPT Paging-Structure Entry를 다음과 같이 변경한 후INVEPT Type을Single-Context로 하여INVEPT명령을 사용해야 합니다.(INVEPT Descriptor에는 수정된EPT Paging-Structure를 직접 또는 간접적으로 참조하는EPTP값이 포함되어야 합니다.)Privilegebits 2:0 을 1에서 0으로 변경- 물리 주소의 bits 51:12 를 변경

Accessed, Dirty Flag가 활성화 된 경우 bit 8(accessed flag) 를 지워야함EPT PDPTE또는EPT PDE의 경우 bit 7 변경(엔트리가 페이지를 매핑하는지 여부를 결정하는 비트)- 게스트 물리 주소(bit 7이 1로 설정된

EPT PDPTE, PDE, PTE)를 변환하는 데 사용되는 마지막EPT Paging-Structure Entry의 경우 bits 5:3 또는 bit 6을 변경합니다. - 게스트 물리 주소(위와 동일)를 변환하는 데 사용되는 마지막

EPT Paging-Structure Entry의 경우 bit 9(dirty flag)가 활성화되어 있으면 지워야 합니다.

[0x05] Conclusion

드디어 Intel SDM 에 있는 VMM 과 연관된 목표한 부분을 끝냈습니다.

다만 EPT 에서 페이징과 관련하여 아직 익숙치 않은 부분이 많습니다.

Paging-Structure 라는 하나의 거대한 구조는 페이징이라는 프로세스에서 필요한 구조들의 집합이란 것은 확실히 이해했습니다.

이에 따라 매핑되느냐(bit 7 = 1) 참조되느냐(bit 7 = 0)에 따라 다른 구조를 사용한다는 것으로 이해했습니다.

매핑이 되는 경우 해당 엔트리가 최종 계산이며, 참조의 경우 또 다른 테이블을 참조하여 엔트리를 찾아갑니다.

어쨋든 어설픈 번역과 이해이기 때문에 해당 문서들은 추가적으로 더 보강할 것 입니다.

※ 페이징과 관련된 내용이 정리되었으며, 아래 링크에서 확인할 수 있습니다.

[0x06] Reference

- Intel 64 and IA-32 Architectures Software Developer’s Manual